# Non-isolated Interleaved High Step-up Converter with Reduced Voltage Multiplier Stages and a Regenerative Turn-off Snubber

Kazuhiro Umetani and Eiji Hiraki Graduate School of Nature Science and Technology Okayama University Okayama, Japan Masayoshi Yamamoto Interdisciplinary Graduate School of Science and Engineering Shimane University Matsue, Japan

Published in: 2015 IEEE Energy Conversion Congress and Exposition (ECCE)

© 2015 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

DOI: 10.1109/ECCE.2015.7309679

# Non-isolated Interleaved High Step-up Converter with Reduced Voltage Multiplier Stages and a Regenerative Turn-off Snubber

Kazuhiro Umetani and Eiji Hiraki Graduate School of Nature Science and Technology Okayama University Okayama, Japan umetani@okayama-u.ac.jp

Abstract—This paper proposes a novel non-isolated high stepup converter suitable for miniaturization by high frequency design. High step-up converters with voltage multipliers are promising for high frequency design because many of them can be free from coupled inductors or transformers, which may lower the voltage gain due to the leakage inductance or may cause significant AC conduction loss in the primary winding. However, two issues can still hinder further miniaturization. One is that many multiplier stages may be needed to achieve extremely high voltage gain. The other is that high switching frequency may be restricted by severe turn-off voltage surge caused by high speed switching. The proposed converter addresses the former by applying a recently reported technique to a non-isolated boost converter. Additionally, the converter addresses the latter by proposing a simple passive regenerative turn-off snubber implementable only by two diodes and a capacitor. Experiments verified that the proposed converter achieves high voltage gain with fewer voltage multiplier stages compared to prior nonisolated high step-up converters. Additionally, the snubber successfully reduced the turn-off surge into half approximately without apparent deterioration of the efficiency.

Keywords—high step-up; voltage multiplier; interleaved boost converter; turn-off snubber; voltage surge

#### I. INTRODUCTION

Recently, photovoltaic cells and fuel cells are attracting increasing attention as promising power sources with low environmental burden. These cells are generally stacked to enhance the voltage. However, highly stacked cells may often deteriorate the electric charge capacity because the worst cell with the least capacity tends to limit the capacity of the whole stack. To address the issue, high step-up converters can be applied to reduce the number of the stacked cells. Nonetheless, adding a converter will expand the volume. Therefore, high step-up converters are required to be miniaturized.

One basic strategy is high frequency design, i.e. to design a converter to operate at high switching frequency. However, basic converter topologies, such as the normal boost converter, the isolated flyback and forward converters, as well as the LLC converters [1]–[3], tend to have difficulties in achieving high voltage gain at high switching frequency.

Masayoshi Yamamoto Interdisciplinary Graduate School of Science and Engineering Shimane University Matsue, Japan

The normal boost converter can suffer from severe switching loss due to large current and voltage stresses to the switching device. The isolated converters can suffer from decrease in the voltage gain because high frequency operation generally suppresses current induction in the secondary winding due to the leakage inductance. The LLC converter can suffer from large resonant current in the primary winding, causing large AC conduction loss particularly at high resonant frequency.

Except for these basic converters, a number of high step-up converter topologies have been proposed [4]–[21]. These topologies can be mainly classified into two categories according to the strategies towards high voltage gain.

One category utilizes coupled inductors or transformers [4]–[11]. This category is beneficial in achieving high voltage gain only by adding turns to the secondary winding. Additionally, many topologies of this category can employ voltage clamping capacitors to reduce voltage stress of the switching devices to a voltage far below the output voltage [4]–[11]. This generally suppresses the switching loss to alleviate the efficiency drop caused by high frequency operation. However, the leakage inductance may suppress the current induction in the secondary winding, or the large AC current in the primary winding may cause significant AC conduction loss, resulting in deterioration of the voltage gain particularly in high frequency operation.

The other category utilizes voltage multipliers or switchedcapacitor multipliers [12]–[21]. Many topologies of this category can be implemented by basic circuit components, such as inductors, capacitors, diodes, and switches. Hence, they can be free from coupled inductors and transformers. Additionally, many topologies [13]–[21] of this category can further reduce voltage stress of the switching devices to a voltage far below the output voltage, alleviating the efficiency drop by high frequency operation. Therefore, this category can be promising for miniaturization by high frequency design.

Nonetheless, this category still suffer from two difficulties: One is that high voltage gain can require many multiplier stages, thus hindering miniaturization; and the other is that severe turn-off voltage surge can appear because of high speed

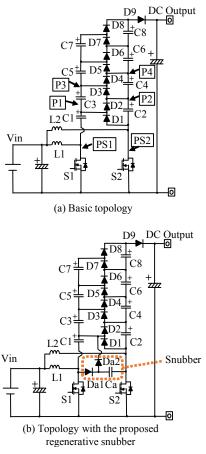

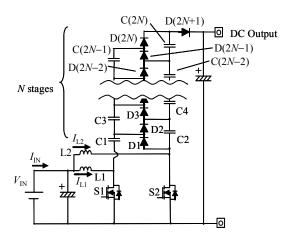

Fig. 1. Proposed converters with 4 stages of a voltage multiplier.

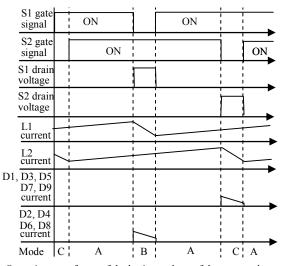

Fig. 2. Operating waveforms of the basic topology of the proposed converter.

switching required for high frequency operation. As for the former difficulty, [20] has proposed a promising converter to reduce the multiplier stages. However, application of this converter is limited because it does not have common ground between the input and the output.

The purpose of this paper is to address these two difficulties. The former is addressed by improving the prior converter [20]; and the latter is addressed by proposing a novel passive

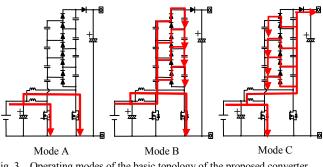

Fig. 3. Operating modes of the basic topology of the proposed converter.

regenerative turn-off snubber. As a result, this paper proposes a non-isolated high step-up converter with reduced voltage multiplier stages and the regenerative snubber. The snubber enables the switching devices to achieve the zero-voltage turnoff, thus suppressing the turn-off voltage surge. Certainly, the prior technique [20] already proposed an active clamp to suppress the surge. However, our snubber is beneficial in simple implementation because our snubber is composed of only three passive components, i.e. two diodes and a capacitor.

The following discussion is divided into three sections. Section II discusses the operational principles of the proposed converter theoretically. Section III presents experiments to confirm the operational principles. Finally, Section IV presents the conclusions.

#### II. PROPOSED CONVERTER

#### A. Circuit Overview

Figure 1 illustrates the circuit topologies of the proposed converter. Figure 1(a) is the basic topology, configured as a two-phase interleaved boost converter with a voltage multiplier. This configuration is similar to the prior high stepup converter reported in [20]. However, the following two differences exist in the circuit topology: One is that rectifying diode D9 is added so that this converter has common ground between the input and the output; and the other is that capacitor C1 is connected to switch S1 instead of switch S2. Capacitor C1 has the positive voltage on its terminal connected to capacitor C3, contrary to [20]. This difference enhances the voltage gain of the proposed converter slightly more than the prior converter, as shown later.

Figure 1(b) further incorporates the passive regenerative turn-off snubber composed of diodes Da1, Da2, and capacitor Ca. This snubber achieves zero-voltage turn-off of both S1 and S2 without additional control algorithms of the switches. Diodes Da1 and Da2 can have small DC current rating because the current flows through the snubber only during the turn-off of S1 and S2. Snubber capacitor Ca also has much smaller capacitance compared to capacitors C1-C8 because Ca is used only to suppress rising speed of the drain voltage of S1 and S2 during their turn-off. Therefore, the proposed snubber can avoid adding significant volume.

#### B. Operating Principles of the Proposed Converter

This subsection discusses the circuit behaviors of Fig. 1(a) to clarify the operating principles of the proposed converter.

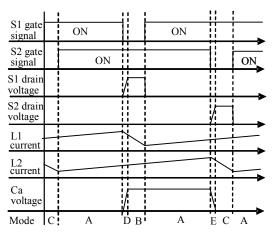

Fig. 4. Operating waveforms of the proposed converter with the regenerative snubber.

The proposed converter operates similarly to the prior converter [20]. Operating waveforms are presented in Fig. 2. The on-state of S1 and S2 must overlap each other. Therefore, the switches are operated at duty cycles greater than 0.5 with 180 degree phase shift. Consequently, operation of the proposed converter consists of the following three modes presented in Fig. 3.

In mode A, both of the switches are in the on-state. The input voltage is applied to both inductors L1 and L2 to increase the current of the inductors.

In mode B, S1 is in the off-state; and S2 is in the on-state. The current of L1 flows through diodes D2, D4, D6, and D8 to charge C2, C4, C6, and C8. The current of L2 continues to increase, whereas the current of L1 decreases.

In mode C, S1 is in the on-state; and S2 is in the off-state. The current of L2 flows through diodes D1, D3, D5, and D7 to charge C1, C3, C5, and C7. At the same time, a part of the current of L2 flows through D9 to charge the output capacitor. The current of L1 continues to increase, whereas the current of L2 decreases.

#### C. Regenerative Snubber

Next, this subsection discusses the circuit behavior of Fig. 1(b) to clarify the operating principles of the proposed regenerative snubber. The operation of Fig. 1(b) is similar to that of Fig 1(a). The operation consists of modes A–E. Modes A–C are the same as those of Fig. 1(a) because no current flows in the regenerative snubber. The regenerative snubber works in modes D and E, which are inserted between modes A and B and between modes A and C, respectively. Figure 4 shows the operation waveforms of the regenerative snubber. Figure 5 shows the current patterns in each mode. Hereafter, we explain the operation during modes D and E, respectively.

In mode D, S1 is turned off and the current of L1 flows through Da1 to charge Ca. Thus, rising of the drain voltage of S1 is suppressed to reduce the turn-off voltage surge. Snubber capacitor Ca is entirely charged to the voltage  $V_{C2}-V_{C1}$ , where  $V_{C1}$  and  $V_{C2}$  are the voltage of C1 and C2, respectively. Then, the current of L1 flows through C1, entering mode B.

Fig. 5. Operating modes of the proposed converter with the regenerative snubber.

In mode E, S2 is turned off; and the current of L2 flows through Da2 and C1 to discharge Ca. Thus, rising of the drain voltage of S2 is suppressed to reduce the turn-off voltage surge. After the drain voltage of S2 rises to the voltage  $V_{C1}$ , the current flows to the voltage multiplier, entering mode C. Hence, the charge stored in Ca is discharged to C1 and is finally regenerated as the output power. This indicates that the proposed snubber is regenerative; and therefore, it can suppress the energy loss caused by the snubber.

For effective zero-voltage turn-off, Ca should be entirely discharged to zero voltage before entering mode D; and Ca should be charged to  $V_{C1}$  before entering mode E. These two requirements can be met by achieving the relation  $V_{C2}-V_{C1}=V_{C1}$ . This relation requires the same duty cycle for S1 and S2, as shown later. (This is shown by setting  $D_{S1}$  and  $D_{S2}$  at the same value in (10) and (11), where  $D_{S1}$  and  $D_{S2}$  are the duty cycles of S1 and S2, respectively.) Therefore, the proposed regenerative snubber needs the duty cycles of S1 and S2 to be set at almost same value.

## D. Voltage and Current in Steady Operation

This subsection analyzes the capacitor voltage and the inductor current in the steady operation based on the basic topology of the proposed converter. We generalize our discussion to cover the proposed converter with an *N*-stage voltage multiplier shown in Fig. 6. (Figure 1(a) corresponds to a special case with 4 stages.) For convenience, we assume that L1 and L2 have the same inductance *L* and that all the capacitors in the voltage multiplier have the same capacitance *C*. Furthermore, we assume that the voltage ripple of C1–C(2*N*) is ignorable, as well as the current ripple of L1 and L2. We denote the capacitor voltage as '*V*' with subscript of the capacitor index, and the diode current during mode B or C (either mode in which the current flows through this diode) as '*T*' with subscript of the diode index.

Fig. 6. Basic topology of the proposed converter with an N-stage voltage ultiplier.

According to the current flow of mode B shown in Fig. 3, we have the following relation between the average current through L1 ( $I_{L1}$ ) and the diode current:

$$I_{\rm L1} = I_{\rm D2} + I_{\rm D4} + \dots + I_{\rm D(2N)}.$$

(1)

Similarly, according to mode C, we have the relation between the average current through L2  $(I_{L2})$  and the diode current:

$$I_{L2} = I_{D1} + I_{D3} + \dots + I_{D(2N-1)} + I_{D(2N+1)}.$$

(2)

First, we focus on the average voltage of the capacitors. Equating the total current flow into a capacitor with the time derivative of the average charge in the capacitor, we obtain (3) and (4) for the capacitors C(2k-1) and C(2k), where k is an arbitrary natural number from 1 to N.

$$C \frac{dV_{C(2k-1)}}{dt} = -(1 - D_{S1}) \sum_{n=1}^{N-k+1} I_{D(2N+2-2n)} + (1 - D_{S2}) \sum_{n=1}^{N-k+1} I_{D(2N+1-2n)}, \quad (3)$$

$$C \frac{dV_{C(2k)}}{dt} = (1 - D_{S1}) \sum_{n=1}^{N-k+1} I_{D(2N+2-2n)} - (1 - D_{S2}) \sum_{n=1}^{N-k+1} I_{D(2N+3-2n)}, \quad (4)$$

where  $D_{S1}$  and  $D_{S2}$  are duty cycles of S1 and S2, respectively.

In steady operation, all time derivative terms must vanish. Hence, we obtain the solution of (3) and (4) for the steady operation, using (1) and (2):

$$I_{\rm D1} = I_{\rm D3} = \dots = I_{\rm D(2N-1)} = I_{\rm D(2N+1)} = \frac{I_{\rm L2}}{N+1},$$

(5)

$$I_{\rm D2} = I_{\rm D4} = \dots = I_{\rm D(2N)} = \frac{I_{\rm L1}}{N},$$

(6)

$$(1 - D_{s_2}) \frac{I_{L_2}}{N+1} = (1 - D_{s_1}) \frac{I_{L_1}}{N}.$$

(7)

According to (5) and (7), the output current  $I_{OUT}$  can be expressed as

$$I_{\rm OUT} = (1 - D_{\rm S2})I_{D(2N+1)} = (1 - D_{\rm S2})\frac{I_{\rm L2}}{N+1} = (1 - D_{\rm S1})\frac{I_{\rm L1}}{N}.$$

(8)

Next, we investigate the time derivative of the average current through L1 and L2. The drain voltage of S1 in mode B is equal to  $V_{C2}-V_{C1}$ ; and the drain voltage of S2 in mode C is equal to  $V_{C1}$ . Hence, we obtain

$$L\frac{dI_{\rm L1}}{dt} = D_{\rm S1}V_{\rm IN} - (1 - D_{\rm S1})(V_{\rm C2} - V_{\rm C1} - V_{\rm IN}), \tag{9}$$

$$L\frac{dI_{L2}}{dt} = D_{S2}V_{IN} - (1 - D_{S2})(V_{C1} - V_{IN}), \qquad (10)$$

where  $V_{\rm IN}$  is the input voltage. The voltage relations in the steady operation can be obtained by regarding all time derivative as zero in (9) and (10). As a result, we have

$$V_{\rm C1} = \frac{V_{\rm IN}}{1 - D_{\rm S2}},\tag{11}$$

$$V_{\rm c_2} = \left(\frac{1}{1 - D_{\rm S1}} + \frac{1}{1 - D_{\rm S2}}\right) V_{\rm IN}.$$

(12)

Equations (5) and (6) indicate that all the diodes conduct current in either modes B or C in the steady operation. In mode B, diodes D2, D4, ..., D(2N) conduct current to connect capacitors C3, C5, ..., C(2N-1) in parallel to capacitors C4, C6, ..., D(2N), respectively. Similarly, in mode C, diodes D1, D3, ..., D(2N-1) conduct current to connect capacitors C2, C4, ..., C(2N-2) in parallel to capacitors C3, C5, ..., C(2N-1), respectively. Hence, the capacitor voltage of C2–C(2N) must be the same. As a result, we have

$$V_{\rm C2} = V_{\rm C3} = \dots = V_{\rm C(2N)} = \left(\frac{1}{1 - D_{\rm S1}} + \frac{1}{1 - D_{\rm S2}}\right) V_{\rm IN}.$$

(13)

As mentioned in Subsection II.C, the proposed regenerative snubber needs  $V_{C2}-V_{C1}=V_{C1}$ . This requirement can be met by setting  $D_{S1}$  and  $D_{S2}$  at the same duty cycle D in (11) and (12). In this case, the voltage of the capacitors can be expressed as

$$V_{c1} = \frac{1}{1-D}V_{IN}, \quad V_{c2} = V_{c3} = \dots = V_{c(2N)} = \frac{2}{1-D}V_{IN}.$$

(14)

# E. Voltage Gain

The output voltage  $V_{OUT}$  is equal to the voltage potential of the positive terminal of C(2N) in mode C, if we neglect the forward voltage drop at the diodes. Consequently, the voltage gain G is obtained as

$$G = \frac{N}{1 - D_{\rm S1}} + \frac{N + 1}{1 - D_{\rm S2}}.$$

(15)

This result is consistent with the energy conservation. In fact, we obtain the following relation from (8) and (15), if we denote the input current as  $I_{IN}$ :

$$I_{\rm L1} = \frac{N}{1 - D_{\rm S1}} I_{\rm OUT}, \quad I_{\rm L2} = \frac{N + 1}{1 - D_{\rm S2}} I_{\rm OUT}.$$

$$\therefore I_{\rm IN} = I_{\rm L1} + I_{\rm L2} = GI_{\rm OUT}.$$

(16)

Therefore, as expected, the input energy is equal to the output energy in the steady operation because  $I_{\text{IN}}V_{\text{IN}}=I_{\text{OUT}}V_{\text{OUT}}$ .

If we set  $D_{S1}$  and  $D_{S2}$  at the same duty cycle *D*, the voltage gain *G* can be expressed as

$$G = \frac{2N+1}{1-D}.$$

(17)

As we have seen above, the proposed converter offers slightly larger voltage gain by 1/(1-D) compared to the prior converter [20]. This voltage gain is obtained not merely by adding D(2*N*+1) to the prior converter because the maximum voltage potential in the prior converter is smaller than the output voltage of the proposed converter by  $V_{IN}/(1-D)$ . In fact, the voltage potential of the positive terminal of capacitor C(2*N*) is enhanced by  $V_{C1}$  during mode C in the proposed converter owing to capacitor C1. Therefore, the difference in the voltage gain is contributed not only by adding diode D(2*N*+1) but also by placing C1 in series with S1.

Compared to the prior non-isolated converters with multistage voltage multipliers [14], [16]–[18], which have common ground between the input and the output, the proposed converter greatly reduces the number of the voltage multiplier stages. The voltage gain of these prior converters can be expressed as (N+1)/(1-D) or N/(1-D). Therefore, if N is set at a large number, the proposed converter can reduce the stages into half approximately.

#### F. Voltage Stress of the Switches

Next, we analyze the voltage stress  $V_{S1}$  and  $V_{S2}$  of S1 and S2 during their off-state. According to the current flow in modes B and C shown in Fig. 3,  $V_{S1}$  and  $V_{S2}$  are obtained using (11) and (12):

$$V_{\rm S1} = V_{\rm C2} - V_{\rm C1} = \frac{V_{\rm IN}}{(1 - D_{\rm S1})}, \quad V_{\rm S2} = V_{\rm C1} = \frac{V_{\rm IN}}{(1 - D_{\rm S2})}.$$

(18)

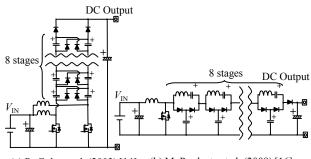

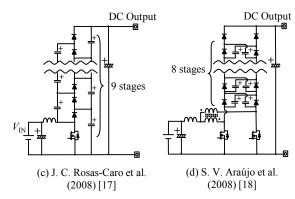

(a) R. Gules et al. (2003) [14] (b) M. Prudente et al. (2008) [16]

Fig. 7. Prior converters employed for comparison of the circuit elements.

TABLE I. COMPARISON OF THE CIRCUIT ELEMENTS.

|           |                     | Proposed                 | Prior Converters |           |           |           |

|-----------|---------------------|--------------------------|------------------|-----------|-----------|-----------|

|           |                     | Converter<br>(Fig. 1(a)) | Fig. 7(a)        | Fig. 7(b) | Fig. 7(c) | Fig. 7(d) |

| Capacitor | Number of elements  | 8                        | 16               | 16        | 17        | 16        |

|           | Max.<br>Voltage [V] | 89                       | 44               | 356       | 44        | 44        |

| Diode     | Number of elements  | 9                        | 18               | 17        | 17        | 18        |

|           | Max.<br>Voltage [V] | 89                       | 89               | 44        | 44        | 89        |

| Switch    | Number of elements  | 2                        | 2                | 1         | 1         | 2         |

|           | Max.<br>Voltage [V] | 44                       | 44               | 44        | 44        | 44        |

| Inductor  | Number of elements  | 2                        | 2                | 9         | 1         | 2         |

| fThe output voltage and the duty cycle are 400V and 75%, respectively.             |

|------------------------------------------------------------------------------------|

| <b>∔</b> The input and output smoothing capacitors are not included in this table. |

This result indicates that the voltage stress is far smaller than the output voltage  $V_{\text{OUT}}$ . In fact, if we assume the same duty cycle for S1 and S2, the ratios of the voltage stress to  $V_{\text{OUT}}$  are obtained from (17) and (18) as

$$\frac{V_{\rm s1}}{V_{\rm out}} = \frac{V_{\rm s2}}{V_{\rm out}} = \frac{1}{2N+1}.$$

(19)

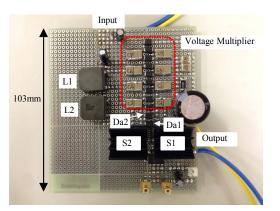

Fig. 8. Prototype of the proposed converter with the regenerative snubber. (Capacitor Ca is mounted on the bottom side.)

| TABLE II.           | SPECIFICATIONS OF THE PROTOTYPES |  |  |

|---------------------|----------------------------------|--|--|

| Input Voltage       | 11V (approx.)                    |  |  |

| Max. Output Voltage | 400V                             |  |  |

| Max. Output Power   | 90W                              |  |  |

| Switching Frequency | 200kHz                           |  |  |

| Gating Voltage      | 10V                              |  |  |

| L1, L2              | 27uH (Sagami 7G14A-270M)         |  |  |

| S1, S2              | FDP52N20 (Fairchild)             |  |  |

| D1-D8, Dt, Ds1, Ds2 | ES3DB-13-F (Diodes Zetex)        |  |  |

| C1-C8               | 1uF (Murata GRM55DR72E105KW01L)  |  |  |

| Cs                  | 3nF (Murata GRM21AR72E332KW01D)  |  |  |

# G. Comparison of the Circuit Elements

As we have seen above, the proposed converter can reduce the voltage multiplier stages. This reduces the number of the circuit elements, which can lead to miniaturization of the converter. The purpose of this subsection is to estimate the reduction effect of circuit elements in comparison with the prior non-isolated converters with multi-stage voltage multipliers.

Figure 7 shows the prior non-isolated converters for comparison, reported in [14], [16]–[18]. (The converter reported in [20] is not included because this converter does not have common ground with the input and the output.) These prior converters are all designed to achieve the voltage gain of 36 at the same duty cycle of 75%. (All switches are assumed to operate at the same duty cycle.) In order to calculate the voltage stress of the circuit elements, we set the maximum output voltage at 400V.

Table I shows comparison of the number of the circuit elements, as well as their maximum voltage stress. The result reveals that the proposed converter reduces the number of capacitors and diodes approximately into half, owing to reduction in the voltage multiplier stages. On the other hand, the voltage stress of the capacitors and diodes are doubled compared to the prior converters. Therefore, if increase in the voltage stress does not lead to significant increase in the

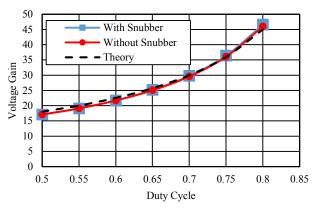

Fig. 9. Relation between the voltage gain and the duty cycle in the proposed converter. The same duty cycle was set for S1 and S2.

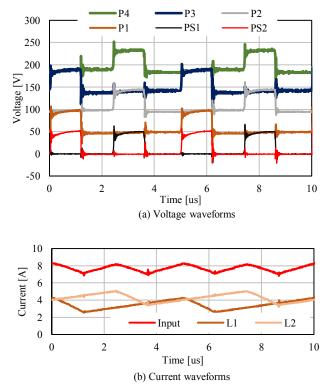

Fig. 10. Voltage and current waveforms of the proposed converter without the snubber. The output was set at 400V, 75W. Measurement points P1-P4, PS1, and PS2 are shown in Fig. 1(a).

volume of the circuit elements, the proposed converter can effectively miniaturize high step-up converters.

#### **III. EXPERIMENT**

#### A. Prototypes

In order to verify the operating principles of the proposed converter, we tested two prototypes: One has the configuration of Fig. 1(a), and the other has the configuration of Fig. 1(b). Figure 8 shows the photograph of the prototype of Fig. 1(b). Table II shows the specifications of the prototypes. Switches S1 and S2 were operated at the same duty cycle. The switching frequency was set at 200kHz.

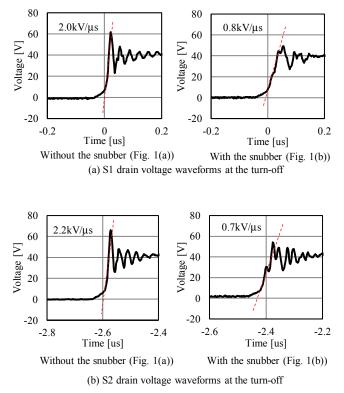

Fig. 11. Comparison of the rising speed of the drain voltage at the turn-off between with and without the snubber. (The output was set at 400V, 75W.)

# B. Voltage gain

Figure 9 shows the dependency of the voltage gain on the duty cycle. The input was set at 11V, 75W; and the duty cycle was varied from 5% to 80%. Accordingly, the output voltage was changed from 200V to 500V.

The results were found to agree well with the theoretical voltage gain calculated according to (17). In fact, the theory predicted the experimental voltage gain within an error of 5%.

# C. Operating Waveforms of the Proposed Converter

Figure 10 shows the voltage and current waveforms of the prototype without the regenerative snubber, when the output was set at 400V, 75W. The voltage waveforms were measured at the points P1–P4, PS1, and PS2 shown in Fig. 1(a). The duty cycle was set at 75%.

The result revealed that the voltage waveforms were consistent with the theory. According to (14), we expected that  $V_{C1}$  is equal to 44V and  $V_{C2}-V_{C8}$  are equal to 89V. The experimental waveforms were close to the theoretical values because the average voltage of C1, C2, C3 and C4 were 48.1V, 96.2V, 92.4V, and 90.0V, respectively. According to (19), we also expect that  $V_{S1}$  and  $V_{S2}$ , i.e. the drain voltage of S1 and S2 during their off-state, are equal to 44V. The experimental waveforms were also close to the theoretical value.

The current waveforms of the inductors L1 and L2 were also consistent with the theory. According to (7), we expected that the average current through L1 ( $I_{L1}$ ) is 0.8 times as large as the average current through L2 ( $I_{L2}$ ). The experimental

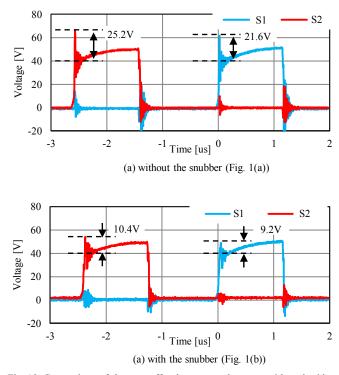

Fig. 12. Comparison of the turn-off voltage surge between with and without the proposed snubber. (The output was set at 400V, 75W.)

Fig. 13. Comparison of the efficiency between with and without the proposed snubber. (The output was set at 400V.)

waveform verified the theory because  $I_{L1}$  and  $I_{L2}$  were 3.4A and 4.3A, respectively.

# D. Turn-off Voltage Surge

Next, we compared the rising speed of the drain voltage at the turn-off between with and without the regenerative snubber to verify the operation principles of the snubber. The output was set at 400V, 75W; and the duty cycle was set at 75%. The results are presented in Fig. 11. The result indicates that the drain voltage of both S1 and S2 rose slowly at the turn-off in the prototype with the regenerative snubber. This result is consistent with the operation principles discussed in the previous section.

The turn-off voltage surge was also found to be suppressed in the prototype with the snubber. Figure 12 compares the drain voltage waveforms of S1 and S2 between with and without the snubber. As a result, the voltage surge was successfully suppressed approximately into half in the prototype with the snubber.

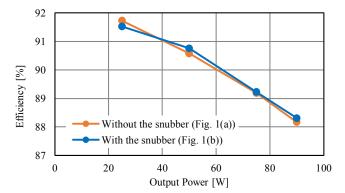

# E. Efficiency

Figure 13 shows the experimental result of the efficiency of the prototypes, when the output was set at 400V and the duty cycle was set at 75%. As seen from the figure, the prototypes showed efficiency higher than 88%.

According to the theory, the regenerative snubber achieves soft-switching at the turn-off of both S1 and S2. Hence, we expected improvement of the efficiency by the snubber. As a result, however, any apparent improvement was scarcely found in Fig. 13. The reason is not cleared in this paper. As a possible reason, reduction in the turn-off switching loss may be canceled by the conduction loss generated in the regenerative snubber. Nonetheless, it should be pointed out that the result does not negate usefulness of the proposed snubber because the snubber successfully reduced the turn-off voltage surge by small additional circuit without apparent reduction of the efficiency.

## IV. CONCLUSIONS

Photovoltaic cells and fuel cells often requires a small-sized high step-up converter in order to minimize the number of the stacked cells. This paper proposed a non-isolated high step-up converter with reduced voltage multiplier stages and a passive regenerative turn-off snubber as a promising candidate. The proposed converter has the following attractive features.

- High frequency design is easy because no coupled inductor nor transformer is used.

- Voltage stress of the switches can be far smaller than the output voltage.

- High voltage gain is achieved with fewer voltage multiplier stages compared with the prior non-isolated converter topologies.

- The turn-off voltage surge can be reduced by small passive additional circuit without apparent reduction of the efficiency.

Experimental results successfully verified the operating principles. The results support that the proposed converter is promising for applications of renewable energy sources.

#### ACKNOWLEDGMENT

We wish to thank DENSO CORPORATION for supporting the experiment of this work. Particularly, we are grateful to Takanari Sasaya and Tomonori Kimura, DENSO CORPORATION, for helpful discussions.

#### REFERENCES

B. M. Han, J. Y. Lee, and Y. S. Jeong, "Power conditioning system for fuel cell with 2-stage DC-DC converter," inProc. Appl. Power Electron. Conf. Expo.(APEC), 2010,Palm Springs, CA, pp. 303-308.

- [2] R. Yu, G. K. Y. Ho, B. M. H. Pong, B. W. K. Ling, and J. Lam, "Computer-aided design and optimization of high-efficiency LLC series resonant converter," *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3243-3256, Jul. 2012.

- [3] J. B. Lee, J. K. Kim, J. H. Kim, J. I. Beak, and G. W. Moon, "A highefficiency PFM half-bridge converter utilizing a half-bridge LLC converter under light load conditions," *IEEE Trans. Power Electron.*, vol. 30, no. 9, Sept. 2015.

- [4] J. Beak, M. Ryoo, T. Kim, D. Yoo, and J. Kim, "High boost converter using voltage multiplier," in *Proc. 31th Annu. Conf. IEEE Ind. Electron.* Soc. (IECON2005), pp. 567-572

- [5] R. Wai and R. Duan, "High step-up converter with coupled-inductor," *IEEE Trans. Power Electron.*, vol. 20, no. 5, pp. 1025-1035, Sept. 2005.

- [6] W. Li, J. Wu, D. Wang, Y. Deng, and X. He, "A family of interleaved DC/DC converters deduced from a basic cell with winding-coupled inductors for high step-up/step-down conversions," in *Proc. Power Electron. Specialists Conf.*, Orland, FL, 2007, pp. 2335-2340.

- [7] W. Li and X. He, "A family of interleaved DC-DC converters deduced from a basic cell with winding-cross-coupled inductors (WCCIs) for high step-up or step-down conversions, *IEEE Trans. Power Electron.*, vol 23, no. 4, pp. 1791-1801, Jul. 2008.

- [8] W. Li, Y. Zhao, Y. Deng, and X. He, "Interleaved converter with voltage multiplier cell for high step-up and high efficiency conversion," *IEEE Trans. Power Electron.*, vol. 25, no. 9, pp. 2397-2407, Sept. 2010.

- [9] S. Araujo, R. Torrico-Bascope, and G. Torrico-Bascope, "Highly efficient high step-up converter for fuel-cell power processing based on three-state commutation cell," *IEEE Trans. Ind. Electron.*, vol. 57, no. 6, pp. 1987-1997, Jun. 2010.

- [10] C. Pan and C. Lai, "A high-efficiency high step-up converter with low switch voltage stress for fuel-cell system applications," *IEEE Trans. Ind. Electron.*, vol. 57, no. 6, pp. 1998-2006, Jun. 2010.

- [11] W. Li, X. Xiang, C. Li, W. Li, and X. He, "Interleaved high step-up ZVT converter with built-in transformer voltage doubler cell for distributed PV generation system," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 300-313, Jan. 2013.

- [12] R. D. Middlebrook, "Transformerless DC-to-DC converters with large conversion ratios," *IEEE Trans. Power Electron.*, vol. 3, no. 4, pp. 484-488, Oct. 1988.

- [13] B. Axelrod, Y. Berkovich, and A. Ionovici, "Transformerless DC-DC converters with a very high DC line-to-load voltage ratio," in *Proc. 2003 Intl. Symp. Circuits Systems*, vol. 3, pp. 435-438.

- [14] R. Gules, L. L. Pfitscher, and L. C. Franco, "An interleaved boost dc-dc converter with large conversion ratio," in *Proc. 2003 Intl. Symp. Ind. Electron.*, vol. 1, pp. 411-416.

- [15] Y. Jiang and M. M. Javonovic, "Interleaved boost converter with intrinsic voltage-doubler characteristic for universal-line PFC front end," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1394-1401, Jul. 2007.

- [16] M. Prudente, L. L. Pfitscher, G. Emmendoerfer, E. F. Romaneli, and R. Gules, "Voltage multiplier cells applied to non-isolated DC-DC converters," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 871-887, Mar. 2008.

- [17] J. C. R. Caro, J. M. Ramirez, and P. M. G. Vite, "Novel DC-DC Multilevel boost converter," in *Proc. 2008 Power Electron. Specialists Conf.*, Rhodes, pp. 2146-2151.

- [18] S. V. Araujo, R. P. T. Bascope, G. V. T. Bascope, and L. Menezes, "Step-up converter with high voltage gain employing three-state switching cell and voltage multiplier," in *Proc. 2008 Power Electron. Specialists Conf.*, Rhodes, pp. 2271-2277.

- [19] E. H. Ismail, M. A. Al-Saffar, A. J. Sabzali, and A. A. Fardoun, "A family of single-switch PWM converters with high step-up conversion ratio," *IEEE Trans. Circuit Syst. I*, Reg. Papers, vol. 55, no. 4, pp. 1159-1171, May 2008.

- [20] P. Kim, S. Lee, J. Park, and S. Choi, "High step-up interleaved boost converters using voltage multiplier cells," in *Proc. 2011 Intl. Conf. Power Electron.*, Jeju, Korea, pp. 2844-2851.

- [21] J. C. R. Caro, H. L. T. Espinosa, F. M. David, A. V. Gonzalez, "A hybrid interleaved/switched-capacitor boost converter," in *Proc. 2013 IEEE Energy Conversion Congr. and Expos*, Denver, CO, pp. 797-804.